Das Projekt Digital Autonomy with RISC-V in Europe, Special Grant Agreement 1 (DARE SGA1), leitet offiziell die erste Phase einer wichtigen Initiative ein. Es gilt, europäische Prozessoren und Rechensysteme der nächsten Generation zu entwickeln. Dazu gehört ein optimiertes Software-Ökosystem, das für Anwendungen in Forschung und Industrie konzipiert ist.

Unterstützt von EuroHPC, einem Gemeinschaftsunternehmen der Europäischen Union, und koordiniert vom Barcelona Supercomputing Center (BSC-CNS), vereint DARE SGA1 38 führende Partner aus ganz Europa. Das Gemeinschaftsunternehmen wird vom Horizon Europe Forschungs- und Innovationsprogramm der Europäischen Union getragen. Ferner sind Deutschland, Spanien, die Tschechische Republik, Italien, die Niederlande, Belgien, Finnland, Griechenland, Kroatien, Portugal, Polen, Schweden, Frankreich und Österreich beteiligt.

Volle Kontrolle über kritische Recheninfrastruktur

Mit einem Budget von 240 Mio. Euro für die erste Phase bildet dieses Drei-Jahres-Projekt einen Teil der sechsjährigen DARE-Initiative. DARE SGA1 soll einen vollständigen europäischen Supercomputing-Hardware- (HW) und Software (SW)-Stack für HPC und KI aufbauen, der in Europa konzipierte und entwickelte leistungsstarke und energieeffiziente Prozessoren enthält. Die Initiative ist eine direkte Antwort auf Europas strategischen Bedarf an digitaler Souveränität. Der Kontinent soll die volle Kontrolle über seine kritische Recheninfrastruktur haben. Jedes Unternehmen, nicht nur die großen Player, braucht Zugang zur benötigten Rechenleistung. KI-Entwickler sollen auf der Grundlage ihrer Innovationskraft konkurrieren, nicht nur aufgrund ihres Zugangs zu Chips oder der Größe ihrer Finanzkraft.

Aufbau des Software-Stacks als übergeordnetes Projektziel

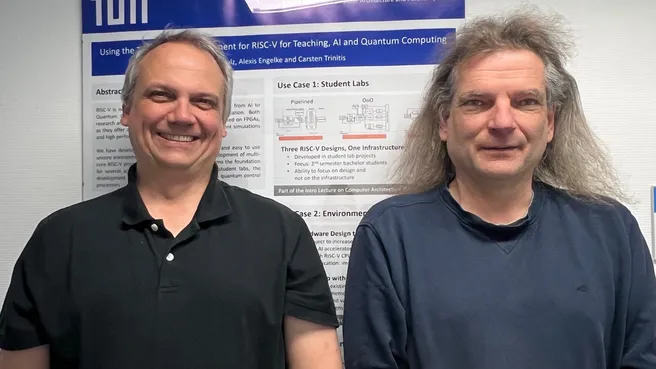

Die Auftaktveranstaltung am 10. und 11. März 2025 im Barcelona Supercomputing Center zeigte das übergeordnete Projektziel: den Aufbau des Software-Stacks, der für eine kommerziell lebensfähige Made-in-Europe-HPC-Chipindustrie und die Beschaffung künftiger EU-Supercomputer mit diesen Chips erforderlich ist. Eine maßgebliche Aufgabe übernimmt hierbei die TUM School of CIT: Unter der Leitung von Carsten Trinitis (Professur für Computer Architecture and Operating Systems in Heilbronn) und Martin Schulz (Professur für Rechnerarchitektur und Parallele Systeme in Garching) soll der Open Source Debugger gdb an die im Projekt entwickelten Instruktionserweiterungen für RISC-V angepasst und in die parallele HPC-Infrastruktur integriert werden. “Dies ist ein wichtiger Schritt in Richtung europäischer HPC-Systeme und wir freuen uns, daran mitwirken zu können”, erläutern die beiden Professoren.